Other Parts Discussed in Thread: TXS0108E

Hi Team,

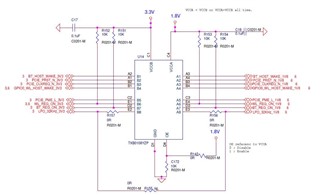

My customer is designing TXB0108, the schematic as below.

PCIE_CLKREQ_N is an open drain at A side, and customer want to set it low from A side.

However the min voltage at B side always around 0.5V (customer need lower than 0.45V) even they pull down to GND.

Is this a normally scenario? Or how can customer modify it so that B side can output lower 0.4V?

Thanks !

Kai