Other Parts Discussed in Thread: SN74LVC1G04

Dear TI experts,

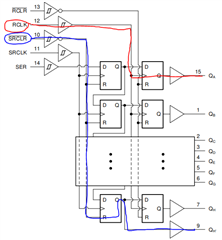

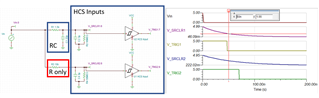

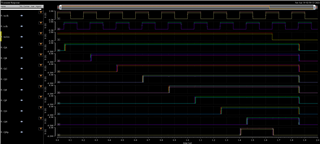

we want to use a chain of SN74HCS594 devices as an IO expander controlled via SPI. The clock of the parallel output register (of all devices in the chain) will be connected to the !CS signal. It would be convenient for us to clear the shift register by !SRCLR while !CS is high (e.g. by using an inverter), to have a defined shift register content when communication is restarted.

Is there a timing requirement after the rising edge of RCLK until the shift register is cleared by !SRCLR, so that the (un-cleared) shift register contents are stored in the output register?

I am aware of the "!SRCLR low before RCLK↑" setup time specification, but I think that is the time required to copy the cleared shift register contents to the output register, so all outputs low. Correct?