Other Parts Discussed in Thread: TINA-TI, SN74AXC1T45, , SN74AVC4T245

Hello,

While I look into how LSF device works, I ran into an e2e thread (please find the original thread) and I have a question.

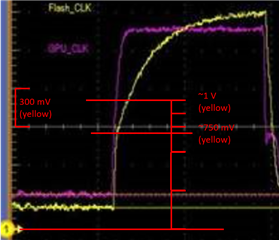

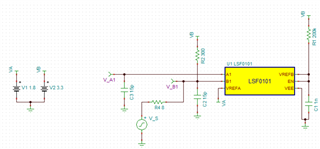

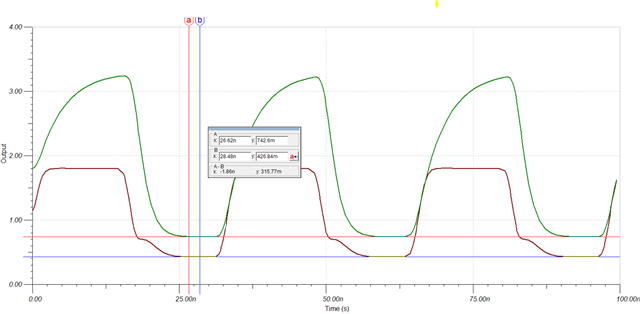

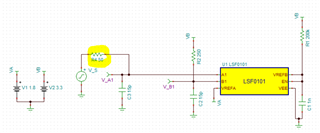

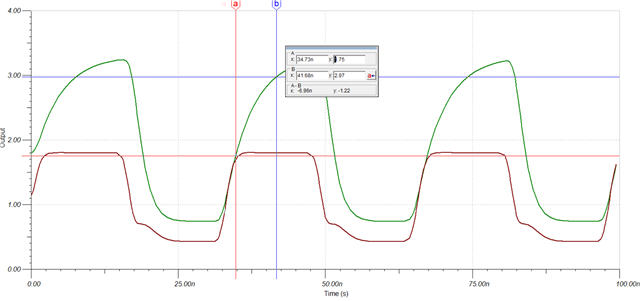

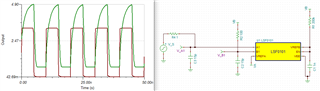

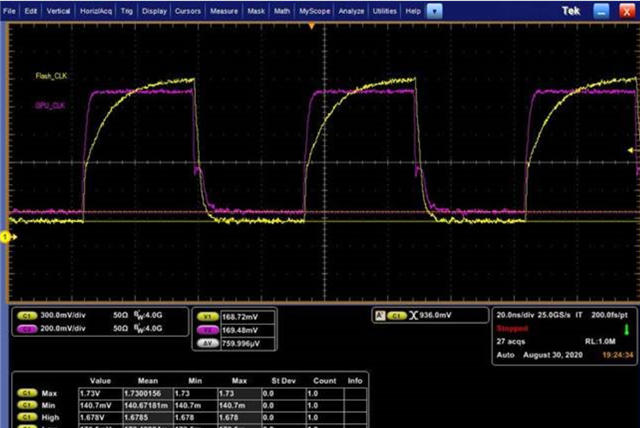

In the original thread, there is a waveform as below - A side (purple) input to B side (yellow) output.

I do not understand why the yellow waveform do not track the purple waveform on its rising edge.

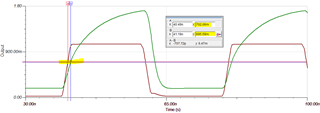

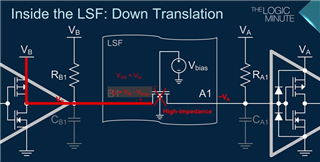

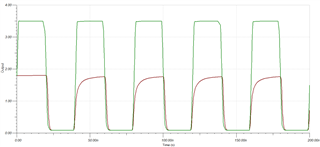

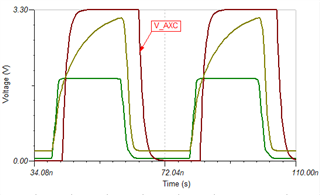

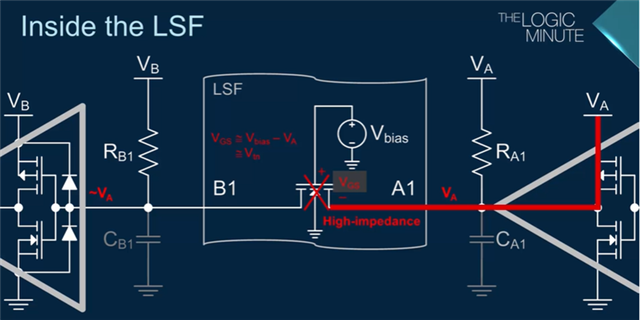

To my knowledge so far : For Translating UP, B1 node voltage would immediately track the A1 node upto ~VA, and then rises following RC (2*RB1*CB1).

Could you help me to find the reason of discrepency between the waveform from the original e2e thread and my undertanding?

Thanks,