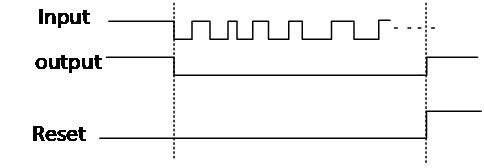

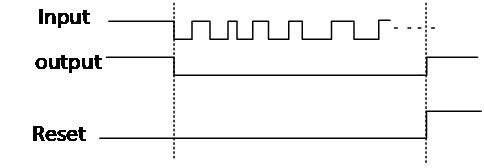

Customer would like to check whether there is any device which can support the below function. They expected the output to turn low at the 1st falling edge of the input signal, and recover only when the reset signal turns high.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Customer would like to check whether there is any device which can support the below function. They expected the output to turn low at the 1st falling edge of the input signal, and recover only when the reset signal turns high.

Hi Clemens,

Thank you for the prompt support. I will further check with customer about this. What if the reset signal is level triggered?

Hi Aki,

I'm not 100% sure what the intended operation is here. Here's what I think is shown:

(1) If the input is steady in the HIGH state, then the output remains in the HIGH state.

(2) As soon as the input switches LOW, the output goes into the LOW state and remains there until the Reset goes HIGH.

(3) My assumption is that the output remains HIGH so long as the Reset remains HIGH

I agree that a D-type Flip-Flop can be used for this operation and would be the simplest solution -- for example, SN74LVC1G74.

I would connect the Input signal to the CLR\ pin of the '1G74, and the Reset signal through an inverter (for example, SN74LVC1G14) to the PRE\ pin. D and CLK could be terminated to ground as I don't think they are really necessary for this circuit -- at least if I understand the operation correctly.

If the reset signal is level triggered, then you need a flip-flop that is triggered on the falling edge, such as the SN74HCS72. Connect /CLK to the input signal, D to GND, /CLR to VCC, and /PRE to the inverted reset signal.