Hello team,

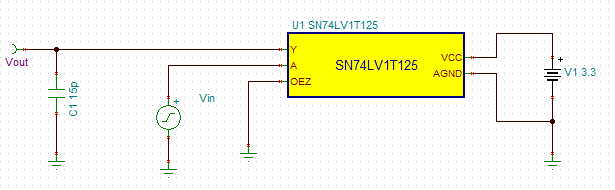

My customer has simulated SN74LV1T125 with below circuit using its behavioral SPICE model provided in its product folder.

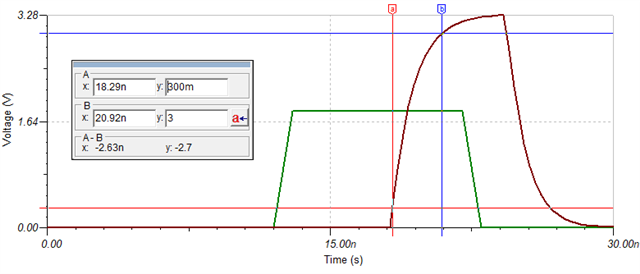

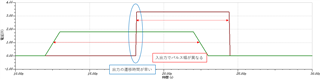

However, the simulation result of transition time is about 300ps and is different from datasheet curve, expected about 3ns.

- Can the model be used for simulating transition time?

- Could you advise me if there is any technic to simulate it properly?

[Simulation schematic]

[Datasheet curve]

[simulation result]

Best regards,