Hi,

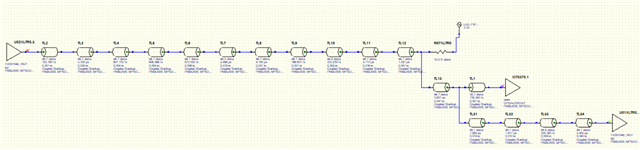

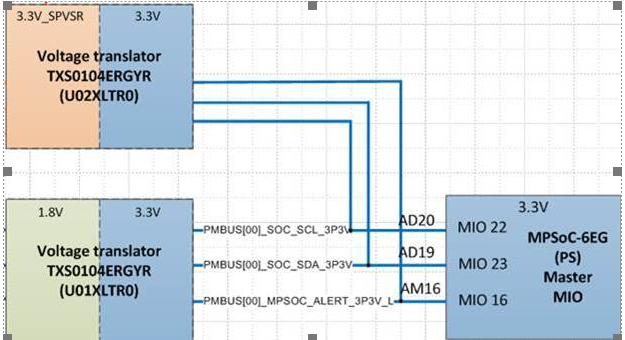

I'm trying to simulate the PMBUS SDA net in Hyperlynx tool between

- Two voltage translators

- When slave - translator is driver & Master - FPGA is receiver

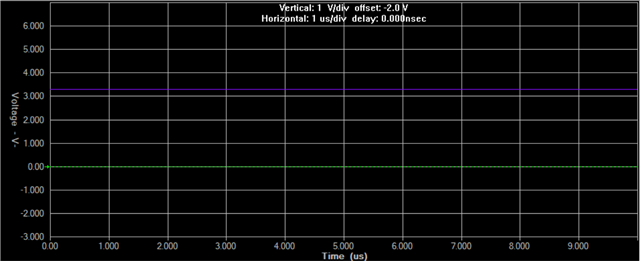

In both the cases, the output is going high to 3.3V but no activity on the bus.

Note: There is an external 10K pull-up resistor on the line, pulled to 3.3V.

Kindly support on this issue.

Thanks