Part Number: TXS0102

Hi team,

My customer use TXS0102 in their project, but they met below issue, could you please help give some suggestions?

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TXS0102

Hi team,

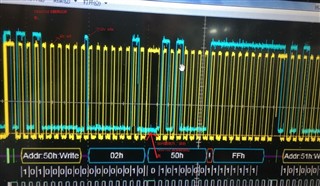

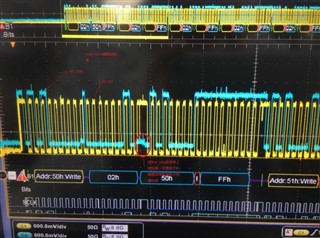

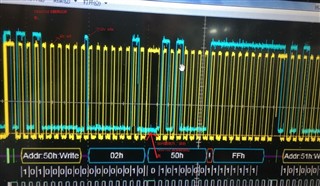

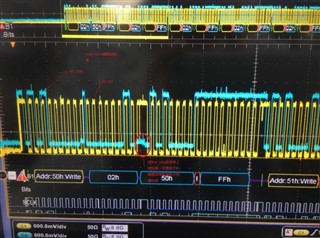

My customer use TXS0102 in their project, but they met below issue, could you please help give some suggestions?

Thank you.

Hey Ivy,

If the signal isn't pulling high, then that means either the host or peripheral isn't releasing the line and making it Hi-z. The TXS device is passive and does not drive Low on its own. If the I2C bus was Hi-z, then the internal pull-ups would pull the line high. Based on the waveforms, I would say its the EEPROM holding it Low. I recommend confirming that those device are actually going into Hi-z.