Other Parts Discussed in Thread: SN74LVC2T45

Hi team,

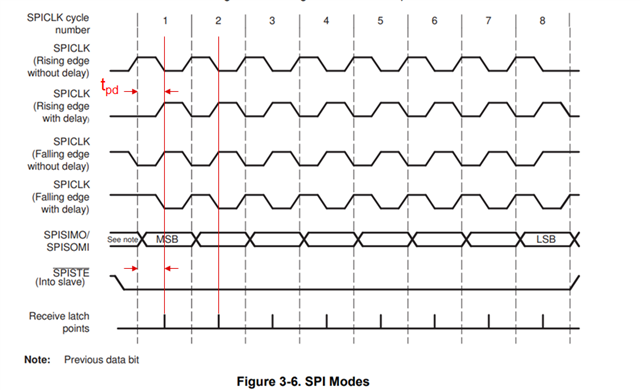

Why could we use 200Mbps data rate @ 3.3V to 5.5V level shifting in spite of signal propagation delay = 0.5~10ns?

SPI master output clock is 200MHz (come from 200Mbps), which is equal to 5ns a period. However, TXU0304-Q1 has 0.5ns~10ns propagation delay for 5.0V to 3.3V transition @TA=125C shown in "7.11 switching characteristics VCCA=3.3+- 0.3." It leads propagation delay > clock period and looks no correct operation.

Regards,

Ochi