Dear Team,

We require one BUS hold circuit for holding two GPIOs in the same state.

Please suggest the part which is having the following requirements.

GPIOs support -2nos

Supply Voltage -3.3V

Regards,

Chitharanjan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Team,

We require one BUS hold circuit for holding two GPIOs in the same state.

Please suggest the part which is having the following requirements.

GPIOs support -2nos

Supply Voltage -3.3V

Regards,

Chitharanjan

Dear Clemens,

Thanks for the suggestion......and also please clarify the below doubts.

Assume, Currently in my design 1A and 2A pin of the SN74LVC2G17 is connected to GPIOs of MCU and during the Deep power down mode GPIOs are goes tri-state, that time what would be the buffer output (1Y and 2Y). ?

And also can you please explain the connection of two resistors?

Just use any buffer (e.g., SN74LVC2G17) and two resistors.

Hello Chitharanjan,

The output state of a buffer is equal to the input state. If your GPIOs are tri-stated, then the only thing driving them will be the buffer, and thus the output and input will remain in the same state.

I assume you want each GPIO to have its own bus-hold circuit. Each resistor goes between xA and xY.

Dear Clemens ,

Thanks for the quick response......

Yes I want each GPIO have its own bus hold circuit.

Assume, I have made resistor connection between 1A and 1Y. what is the use of this parallel resistor connection?

How do I select the resistor value?

will this circuit hold the bus state?

A bus-hold circuit is not in series with the signal, but attached to it at one point; see my schematic above.

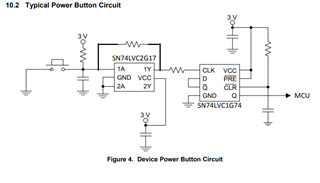

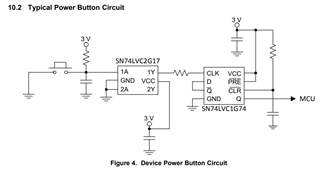

Why are you showing a power-button circuit? Does this have anything to do with your application?

Dear Clemens,

This is example design which is taken from SN74LVC2G17 datasheet.

As per this application design, bus hold circuit is connected in series . Below is the schematic for your reference from SN74LVC2G17 datasheet

Bus hold circuit ha to be attach to the signal (for ex: 1A pin has to be connected to any of the signal which we need to hold, 1Y should be connected to same pin 1A with series resistor).Is my understanding is correct?

That example in the SN74LVC2G17 datasheet does not show a bus-hold circuit but a button debouncing circuit. Ignore it.

Your understanding of the bus-hold circuit is correct.