Other Parts Discussed in Thread: CD74HC165, , SN74HCS165, ISO7740

Dear,

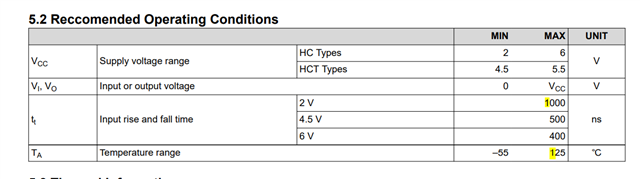

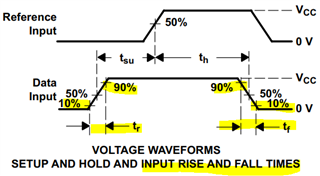

the datasheet Note 2: When Vcc = 2V, Tt =1000nS =1000nS /V x (1.5V-0.5V) ? If Vcc=4.5V, Tt= 500nS/V x (3.15-1.35)=900ns, the chip will not be damaged. As long as it is below 1.35V or above 3.15V, it is safe?

If not, please help to explain, thank you very much ~

Is there a reference value for Vcc=5V?