Hi Team,

If I use SN74AHCT08PWR as a buffer for high speed serial signals of 50 MHz (about 27 ns per bit), is there any problem?

If the high speed signal is inputted to the SN74AHCT08PWR, does the signal fail by the delay?

Beat Regards,

Tom Liu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

If I use SN74AHCT08PWR as a buffer for high speed serial signals of 50 MHz (about 27 ns per bit), is there any problem?

If the high speed signal is inputted to the SN74AHCT08PWR, does the signal fail by the delay?

Beat Regards,

Tom Liu

Hi Liu,

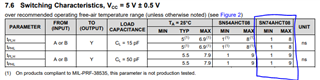

Below is the switching characteristics on the data sheet.

As Clemens said the max prop delay will be 9 ns so you should be fine for this signal.

Regards,

Owen

Hi Clemens and Owen,

Thank you for your answer and I knew 9 ns is fine for my signal.

I have another question:

If the high speed signal is inputted to the SN74AHCT08PWR, does the signal fail by the delay?

Beat Regards,

Tom Liu

for "fail" I mean is there any problem in the signal, or how will the signal be affected.

When the input signal changes, the output signal changes (after the propagation delay). There is no intermediate state.

The speed of the rising/falling edges depends on the load capacitance. For digital signals, these details usually do not matter, but if you care, you can use the IBIS model to simulate the waveforms (or measure the actual device).