Other Parts Discussed in Thread: SN74LV4046A

Hello,

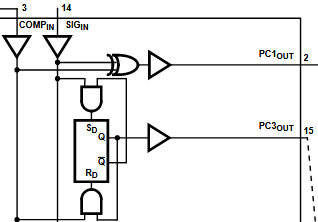

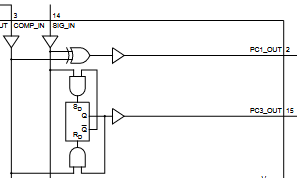

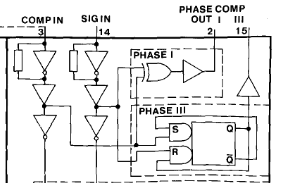

I have a question about the data sheet(Data sheet acquired from Harris Semiconductor SCHS204J) of CD74HC4046A.

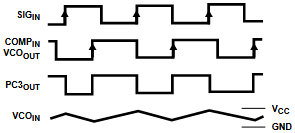

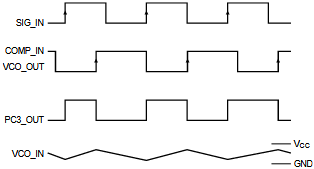

Regarding Phase Comparator 3 (PC3), Figure 7 of the data sheet is an illustration of the operation waveform of PC3. Is this correct?

It seems that SIGIN and COMPIN (VCOOUT) are the opposite compared to the data sheet of other equivalent manufacturers.