Other Parts Discussed in Thread: TPS3808, TLV803E

Hi,

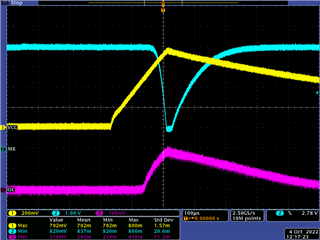

We are using the SN74LVC1G126YZPR in our design. We are observing an unexpected glitch on the SN74LVC1G126 output on Power up which is impacting our board as it triggers a power cycle.

We were expecting the the output to be in High Impedance state on power up. However we observe that on power up, the SN74LVC1G126 pulls the output low for around 50useconds.

As per SN74LVC1G126 datasheet " To ensure the high-impedance state during power up or power down, OE should be tied to GND through a pulldown resistor;"

We have connected the OE pin to 1K pull down resistor on power up. It is also connected to TI 74LVC1G74DC flipflop Q output. The 74LVC1G74DC output rises to around 220mV on power up.

The SN74LVC1G126 is connected to a TPS3808 MR reset input which triggers power cycle. Hence we want to avoid glitch on the SN74LVC1G126 on power up.

- Please advise if there is some way to avoid this glitch on the SN74LVC1G126 on power up.

I have attached the schematic circuit and the waveforms at SN74LVC1G126 Y output, VCC and OE on power up. (Note in the waveform the Y output is labelled MR (Manual Reset))

Thanks

Louis