Other Parts Discussed in Thread: SN74LVC1G17, SN74LVC2G17, SN74AVC4T774

Hi team,

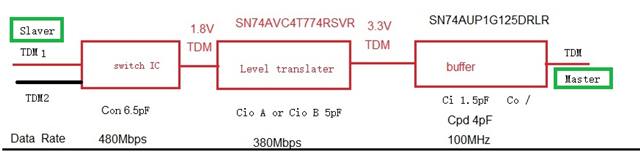

My customer has a TDM data stream designed according to the following block diagram, and the following problems need to be solved:

Buffer is used to enhance I2S (TDM) signal, up to 24MHz

Questions:

Which of the following three devices is more suitable for the customer's application?

|

|

SN74AUP1G125 |

SN74LVC1G17 |

SN74LVC2G17 |

|

Voltage |

0.8~3.6V |

1.65~5.5V |

1.65~5.5V |

|

characteristic |

low power consumption |

High drive capability |

High drive capability |

|

Type |

Tristate output |

Schmidt |

Schmidt |

|

Drive current |

4mA |

24mA |

24mA |

|

|

24mA |

|

|

|

bandwidth |

100MHz |

100MHz |

/ |

|

Cpd |

4pF @ 10MHz |

22pF @ 10MHz |

19pF @ 10MHz |

|

Ci |

1.5pF |

4.5pF |

4pF |

|

Co |

3pF |

/ |

/ |

1. Does Cpd affect the CLK signal? Or is it just the equivalent capacitance when calculating power consumption?

2. SN74LVC2G17 does not indicate the bandwidth. Is it consistent with SN74LVC1G17? What is its output capacitance?

3. Is SN74AUP1G125 the best choice for I2S clock drive (TDM)?

4. The drive current filled in on page P5 of the table in the SN74AUP1G125 specification is 4mA, but page P17 introduces the drive ability of 20mA for high-speed signals. What is the difference between the two drive currents.

5. If there is a level translator on the I2S line, is it necessary to add a buffer? The IO of SN74AVC4T774 has a drive capacity of 8~12mA.

6. Considering the influence capacitance on TDM signal line, how is this capacitance calculated? Con+Cio A (level translator drive isolation, enhancement)? Or Con+Cio A+Ci?