Other Parts Discussed in Thread: SN74HC164

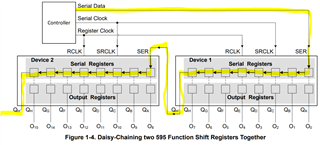

Thanks so much for forums input on the earlier questions on the 54HC595 8-bit shift register. I wanted to ask a related question that addresses the timing of the pulses that output from two cascaded shift registers when the QH’ output is fed into the SER input from the next shift register.

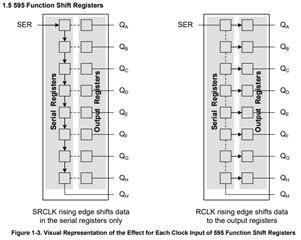

From the timing diagram in the data sheet the output Qb is 1 clock cycle later than Qa, and the output Qc is one clock cycle later than Qb and so on. Qh’ is one half a clock cycle ahead of Qh. So if I feed Qh’ into the SER line of the next shift register, this pulse will come out one clock pulse later at Qa2. So if I line up Qa to Qh, from the first shift register, and Qa2 from the second shift register my thought is that Qa2 from the second shift register won’t be 1 clock cycle away from Qh on the first shift register because it is one half a clock cycle ahead of the last output from the first shift register. So if I want one clock cycle separation between data between cascaded shift registers for the 54HC595 should I be sending Qh’ into the next shift register, or possibly use Qh. I apologies in advance from taking up so much of the TI forum bandwidth. Thanks, Bob Wagner