Other Parts Discussed in Thread: SN74AVC1T45, SN74AUC1G17, 2N7001T, SN74AUP1G17, SN74AUP1T34, TXU0101, SN74LVC1G17

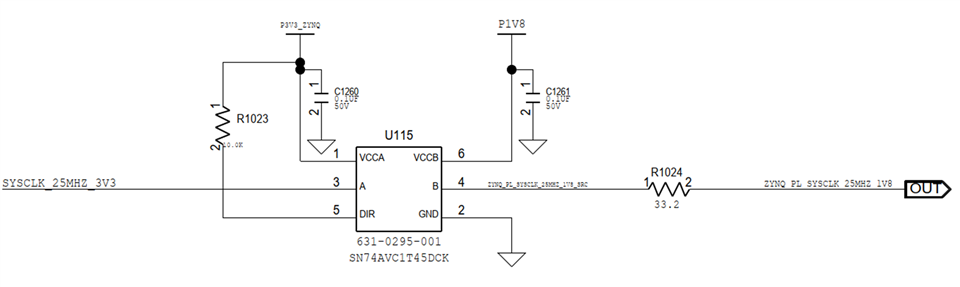

I am planning to use SN74AVC1T45 and SN74AVCH1T45 to level shift 25MHz clocks. An example circuit in our application is shown below.

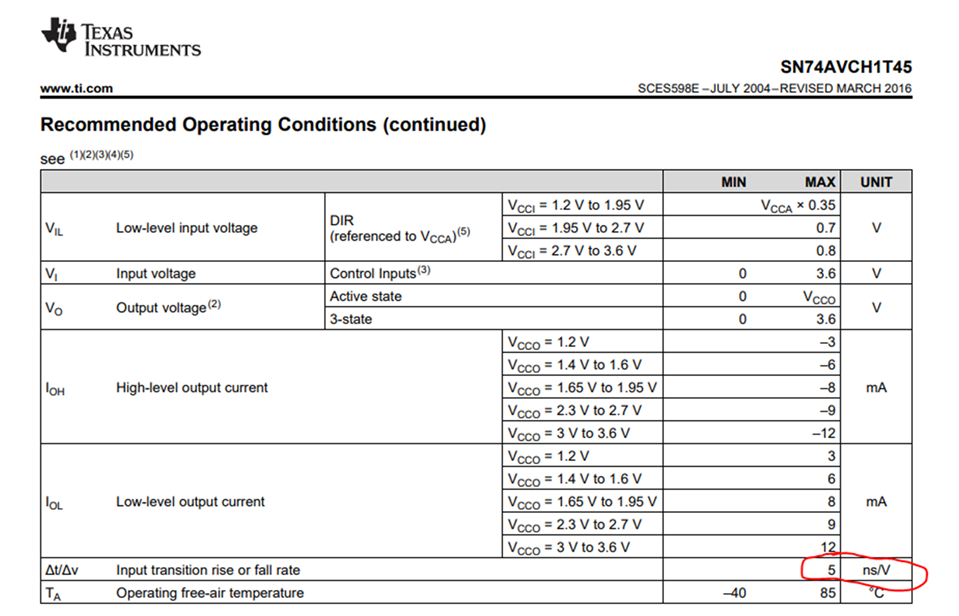

I need clarification on “rise / fall rate” spec. Datasheet shows max dt/dv as 5ns/V. If we consider a clock on 1.8V domain, this translates to a max of 9ns. Does it mean we cannot use this IC to level translate a slower clock like 8kHz which is expected to have a rise time of roughly 12.5us?

The 25MHz clock above has a rise/fall time of 6ns. SN74AVC1T45 / SN74AVCH1T45 should not have any problem dealing with such rise times, right?