Hi,

We are using SN74LVC573ARGYR in various designs. We found a phenomena and we intend to check if issue is being familiar with such a scenario by TI / or cy customers.

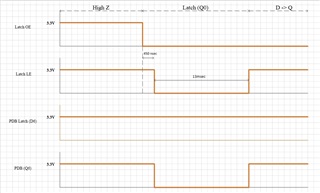

In a specific design, one of the inputs (D6) is connected with Pull-up. When we have a scenario, that the outputs are "High-Z" impedance mode and being switched to "Latch mode", we found that this specific output is not getting High as expected, a fact, which causes our application not working well and fail on normal expected operation. We couldn't find the definition in data sheet and the switching duration is slightly different between device and device (means that sometimes replacement of a device with another one "solves" the issue).

This is not a batch issue, but a phenomena, that we found few % rate of devices, which this issue is more significant than others, looking at different cards from different batches over the last 2 years.

In other applications, which are using this specific device, we don't have a scenario of pull up, so on that applications we don't find any issue. It exists only at the scenario that was described above (D6 --> Q6: Although D6 has a pull-up, when switching from "High Z" mode to "Latch" mode Q6 remains "0". We saw in our work process, that there is a problem with the latch when switching from "High Z" mode to "Latch" mode – the output goes to "0", also there is "1" (pull up) in the Input).

We intend to check if TI / or customers are familiar with the issue. Please help us conclude.

Thank you,

Ido

0" when it is expected to see "1".

0" when it is expected to see "1".