Other Parts Discussed in Thread: SN74HCS125, TLV840, TLV809E

During the device power-up we’ve notice the IO-with bus hold-status is random, when the IO is at high impedance.

We would like to know if, setting the IO at the same voltage than the level shifter, through a pull-up or pull-down, can guarantee a known state for the IO after powering-up the device.

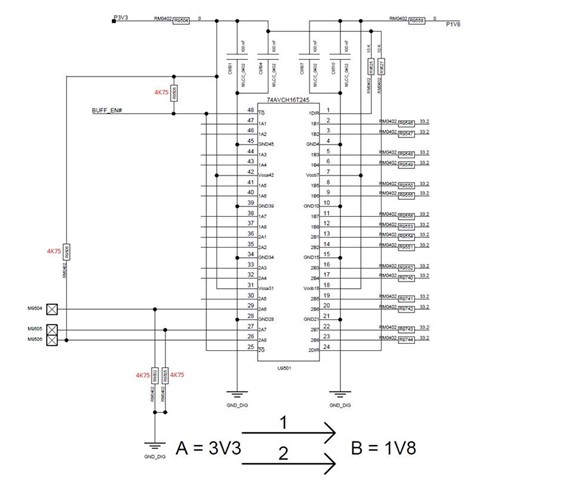

For instance, if we have the following diagram:

We place a pull up/down of 4k75 P3V3 & P1V8 rise at the same time.

- Could we ensure that the bus hold is going to be ALWAYS the following?

*2A6: 0V

*2A7: 0V

*2A8: 3V3

*2B6, 2B7 and 2B8: random (0V or 3V3)

-Will this guaranteed by design (the fact of having the described bus hold status) ? If so, which are the restrictions to meet this situation?