Other Parts Discussed in Thread: SN74LVC244A, SN74HCS244

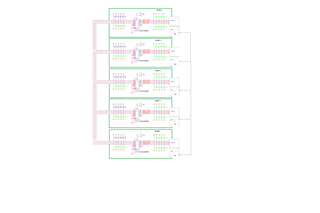

We often use buffers like SN74LVC244A in our boards, especially if we need to interface different boards together with a common bus.

You can look at the sketch below to understand our electrical connection.

We know that SN74LVC244A supports Live Insertion, it has the Ioff parameter and performs a partial power down.

We’ve never seen problems for years but now, in a specific equipment, 3 buffers have been damaged. The 3 components are mounted on 3 different boards, connected together with a common bus.

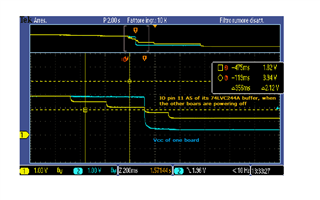

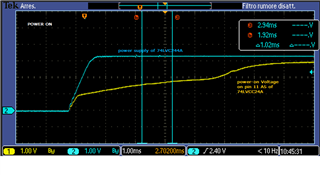

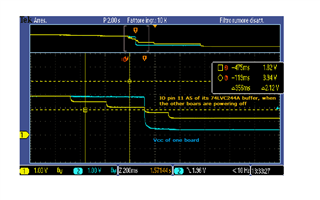

As a consequence, we’ve taken some tests to better understand the behaviour of power supplies and IOs

We believe that one possible damaging cause could be ESD, but after we read better the data sheet some doubts came to us up.

We’ve read something in the TI forum:

https://www.ti.com/lit/an/scba004e/scba004e.pdf?ts=1674562925452

We’ve noticed a special strict requirement in the data sheet about rise and fall time specifications.

Our concern is for what’s going on when VIN power supply falls down, because if the different boards switch their power supplies off at different time points (because of their slighty different thresholds), we actually see an intermedium voltage on the inputs when the SN74LVC244A is still powered (an intermedium level due to a partition among pull-up to 3.3V and pull-“down” on the already unpowered boards).

We’ve noticed that this event happened in the equipment in which 3 ICs SN74LVC244A have broken, and therefore we guess this could be the cause.

Anyway, we tried to damage deliberately another chip but we haven’t been able to see the same damage.

From your point of view has our circuit some critical issues?

Maybe should we use a different family of buffer in our bus implementation? (like HC HCT, that don’t seem to have this timing restriction?)

Thank you in advance for some help