Hi Folks,

Customer would like to use the SN74AUP1G74 to latch a signal during power-on.

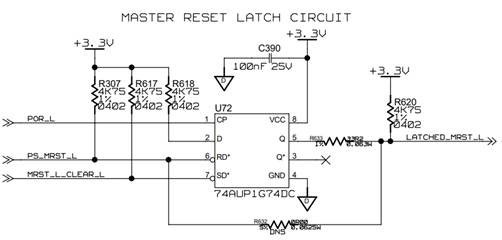

Here’s a snapshot of the circuit:

The question is regarding the power on reset signal connection to the clock input of the device.

The POR_L signal will be low while power rails come up, but as soon as all rails are stable + ~100ms delay, the POR_L signal will go high and stay high as long as the board is powered.

Is it valid to have the clock signal transition low to high once (this will clock in the D value of logic 1) and then stay high continually afterward?

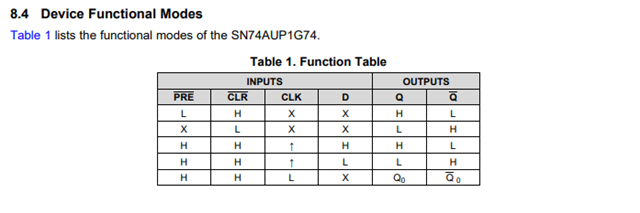

It's probably not a problem however leaving the clock high is not shown as one of the functional modes of the device (see below)

Can we confirm the mode of operation with clock always high is valid?