I have an application where a 74V293 is connected between a microcontroller and a parallel DAC to provide an "elastic" buffer between the two, and to enable the data to the DAC to be transferred at a well-controlled rate.

I've tried with a few variants of the 74V293, including the EP version, and the -6 and -7 standard product speed grades.

Most of the time it works fine but, in this application, about once in every 200 times the data coming out of the FIFO isn't the same as the data going in.

There are no obvious causes. For example, I monitor the full and empty flags, and they're never asserted. All aspects of operation look the same both when the output is as expected, and when it isn't.

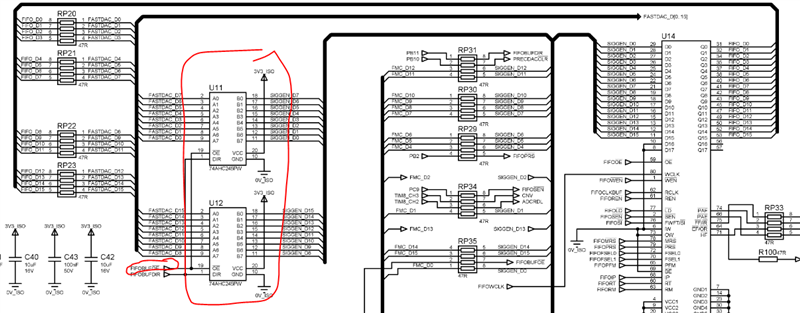

The schematic is shown in this thread: https://e2e.ti.com/support/logic-group/logic/f/logic-forum/874433/sn74v293-unexpected-offset-value

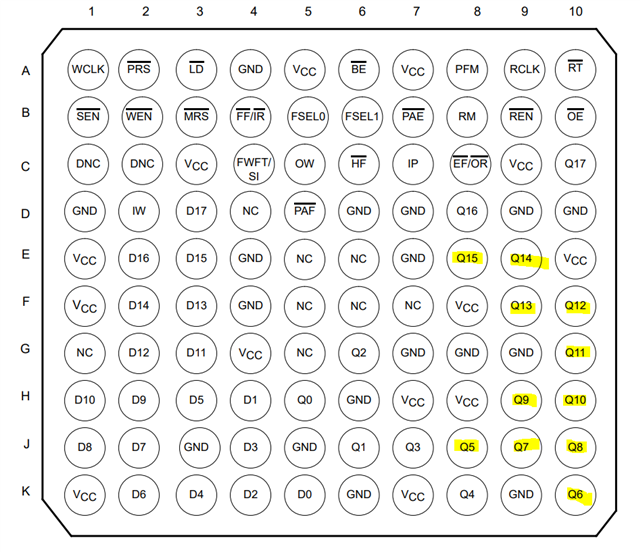

Only D0-D15 and Q0-Q15 are used, since the output drives a 16 bit DAC. The FIFO is configured to operate as a 65536x18 memory.

Data is written to the FIFO in bursts of 8192 values. Readout is at a constant 25MHz. The data written is cached by the microcontroller, so is written at an average rate of about 30M values/s, but is actually written in even shorter bursts that are several cycles in length, and have an even shorter cycle time.

I have, though, tried extending the data setup time so that the write cycles have very conservative timing. That doesn't eliminate the problem.

The programmable empty flag operates sycnhronously, is set to 49152, and is used to trigger a FIFO refill.

I'm limited to a 16 digital + 2 analogue channel MSO for debugging, so I can't easily monitor the input and the output. If I operate this particular MSO so it records a clocked parallel bus, I'm limited to monitoring the enable and clock lines with 14 bits of the data bus.

But, by monitoring the input and output separately, I can see that the data being written to the FIFO is always correct, but that what emerges on the output is sometimes corrupt.

Normally, the data represents a sinusoidal signal. To try and get more of a handle on what's happening, I've tweaked the code so that when this problem occurs, the data written is a linear sequence from 0 to 65535, with an increment of 2 (for reasons of convenience that I won't bother with here).

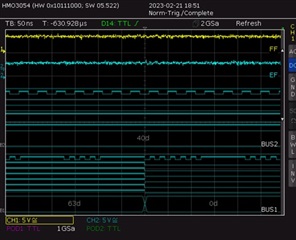

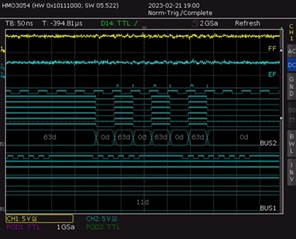

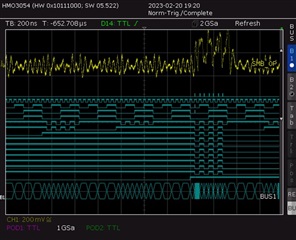

It immediately becomes clear what is happening at the output when this linear test sequence is monitored:

(Not sure why the image quality has deteriorated so much when uploaded, but I think it's clear enough to follow).

The top yellow trace is the DAC output: ignore that. The blue traces are, from the top, REN, RCLK, Q2-Q15.

It's clear that whenever an output bit transitions from low to high, all the lower order bits, as far as and including Q5, then toggle for the next 8 RCLK cycles.

For legibility the screenshot only shows a selection of bit transitions. But the phenomenon occurs at all low to high transitions of Q5-Q15, including the non-existent transition of Q16.

I don't think the glitches on REN are "real". I think they're an artifact of the less-than-ideal probing, which involves a lot of skinny bits of wire making the board into an electrical porcupine.

What is causing the unexpected data pattern?

I've been probing around the circuit and trying different tests for days, and can't come up with any mechanism that could cause this to happen.

Any suggestions would be appreciated.

Colin