Other Parts Discussed in Thread: SN74AUP1G04, SN74AUC1G04, , SN74LVC1G240

The datasheet specifies "data retention only" down to 1.5V. Our understanding is that this means that the circuit will hold the output at the same level if the supply drops into the 1.5V to 1.65V range.

1) However, is there also an expected behavior when considering ramping up into the 1.5V to 1.65V range?

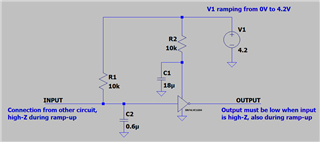

If the input (A) is kept at (or slightly higher than) the the supply voltage when ramping up the voltage, then...

2) what is the expected behavior when passing 1.5V?

3) what is the expected behavior when passing 1.65V?

Is it for instance undefined, or should we perhaps assume that that the output goes high even if the input is as high as the supply?