Dear Team,

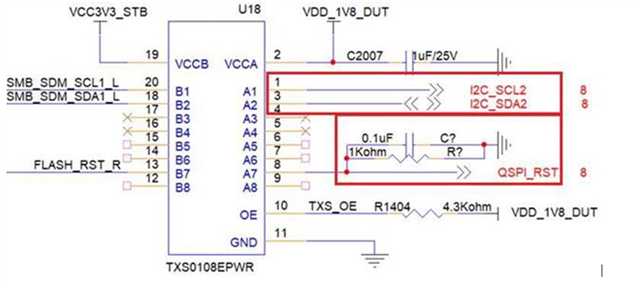

1. The output of the chip has a capacitive load limit: do not exceed the requirement of 30ns for one trigger. However, as shown in the circuit shown in the figure below, QSPI_RST adds a 0.1uF capacitor to ground, and the actual high and low level change time of the signal is about 0.6ms. Please confirm its impact, and is it possible not to care about the 30ns requirement?

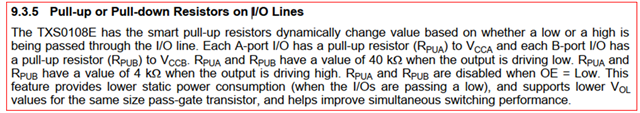

2. As shown in 9.3.5, when the Output is high, there is a 4k pull-up resistor. If the following circuit signal is added with a 1k pull-down, will the actual output high level be 1/5 VCCA (half-high level) and cause the signal to work abnormally?

Many Thanks,

Jimmy