Part Number: TXS0102

Other Parts Discussed in Thread: TXU0102, ISO1541, LSF0102, , ISO1540

当风扇连接时,发现PWM信号波形不正确,高电平被拉低。 现在已经检查过了。它与芯片电路密切相关

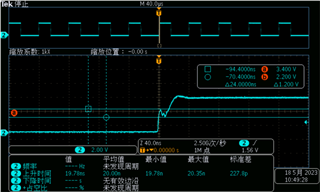

未连接风扇时的PWM波形:

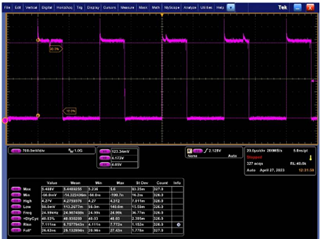

连接风扇时的PWM波形:

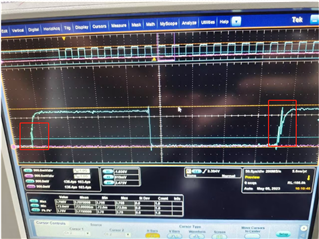

另一个问题:

我们电路在红框中的位置测试波形也存在问题。请帮忙一起检查

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

The TXS has open-drain outputs; the high output voltage is generated by the internal 10 kΩ pull-up resistors. These are not strong enough to complete override the 10 kΩ pull-down in the CTL input.

Use a buffered, unidirectional translator like the TXU0102.

Hi,Is there a good recommendation for PIN TO PIN compatible TXS0102DCUR?

Another question is there is no 10K resistance pull-down. Why is there shock when rising?

when i move away the U16,and test PIN 4,5。the signal is fine。then i think it is not the input signal problem。it may be the ISO1541 problem,its min input current is 3.5ma.what do you think?

Ringing is probably not related to that current.

The TXS is optimized for fast signals, but for I²C, you could just as well use a translator without edge accelerators, such as the LSF0102. But there is no P2P device.

I still don't understand why we have this rising edge problem, right? Is there any way to verify that? Or should I get rid of ISO1541?

However, ISO1541 requires a minimum input current of 3.5mA, and it seems that TXS0102 cannot meet this current。

The TXS is not a buffered device but a passive switch. If you want an output current of 3.5 mA, the device on the other side must be able to sink 3.5 mA.

And the ISO1541 does not require 3.5 mA; it supports output currents up to 3.5 mA.

Hello,So there is something wrong with TXS0102DCUR+ISO1541? Can't fix it now. Need to change the circuit?

Hi Xujunfeng,

What you are experiencing is due to false triggering of the TXS one-shots.

Note that the one-shots are designed to trigger when they detect rising or falling edges. As you can see, reflections / ringing can cause false triggers.

Similar to Clemens' feedback; ringing is also caused by capacitance and inductance of long cables / traces and can also be amplified by unstable GND or VCC voltages.

When you disconnect the ISO device, you are reducing the the lumped capacitance. Hence, you do not see the issue.

If it is not feasible for you to keep the traces minimal similar to section 11.1 of the datasheet, the recommendation would be the TXU0102 for U124 and the LSF0102 for U16 where you don't have one-shots to amplify your ringing, while also having the flexibility to include pull-ups to increase drive strength for signal integrity, thanks.

Best Regards,

Michael.

hello,this is our layout,i do not found problem。and Do you mean that in addition to replacing the chip, you can also try to reduce the pull-up resistor to try to solve the problem?

Hi Xujunfeng,

this is our layout,i do not found problem。

The provided layout do not seem to fully show the layout. How long are the I/O traces? Are the bypass capacitors as close as possible to VCC and GND?

Do you mean that in addition to replacing the chip, you can also try to reduce the pull-up resistor to try to solve the problem?

Yes, the higher the drive; more load can be driven. Hence, increasing drive strength will help with loading issues, thanks.

Best Regards,

Michael.

i change R104-R107 to 4.7K。Waveform above, it seems that reducing the resistance does not solve the problem。what do you think?

Hi Xujunfeng,

Your trace is very long. Note that this will add parasitic capacitance in addition to any load capacitance used.

Also, is blue the input? The rise time is very slow. Are you meeting the datasheet's input transition rate for 10ns/V max? This is also impacted by the lumped capacitance if >70pF total.

Do you notice the signal improving when the frequency is reducing to the lowest you can go?

Best Regards,

Michael.

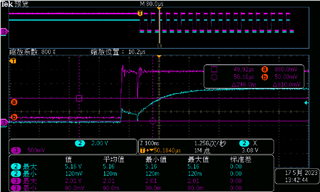

When I changed U14 to TXU0102DCUR and connected the fan, FAN_PWM3 changed into the picture below