Hello,

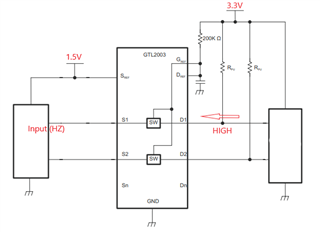

I am wondering how the internal transistor in GTL2003 will work under the following condition.

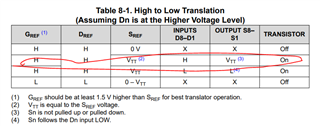

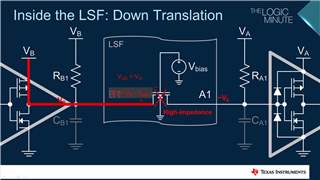

I have already checked Table 8-2 in the datasheet that the output state of that transistor will be VTT and the transistor will be ON. But I don't understand what the transistor does to make Sn go to Vtt level. Could you explain the behavior of the transistor in DETAIL?

Question

1. Could you explain the mechanism by which the transistor turns on under the following conditions?

2. There is no voltage source (pull-up resistor) on the output port (Sn) side. How does the output port (Sn) make the VTT voltage level when the input port (Dn) side is high?

3. If the device connected to the Dn side uses a push-pull port, is it not necessary to use a pull-up resistor on the Dn side?

No pull up resistor on the Sn side.

Thanks.