Hi,

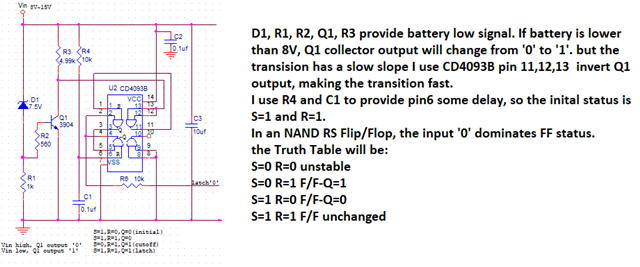

I have trouble to correctly set the CD4093 initial status. I use CD4093B to implement battery cutoff and latch function. See my schematic below.

However, when I test the circuit, After startup (at Vin=10V), I don't get what I expect (initially S=1, R=0, Q=0;when C1 finishes charging S=1, R=1, F/F status unchanged, Q remains 0) . what I get is Q=1.

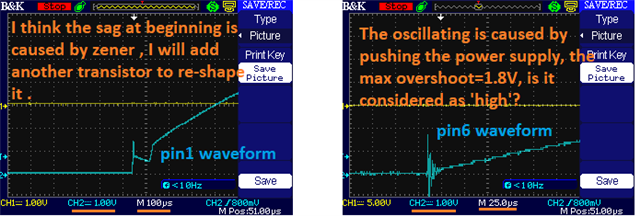

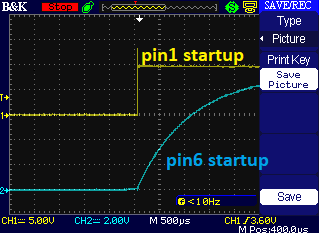

I check the startup waveform, nothing is wrong, see below waveform captured.

I am frustrated. Please help.

Thank you very much.

Chang Cao