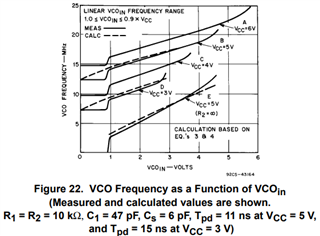

Hello, I am considering using the SN74LV4046A to multiply a base frequency in the order of the 10s kHz to obtain a variable frequency between 2.4 and 9MHz. The reference clock is generated by a microcontroller and the VCO output clock feeds an FPGA which divides it by 128 before sending it to the compare input of the SN74LV4046A. I read the AN "CMOS Phase-Locked-Loop Applications Using the CD54/74HC/HCT4046A and CD54/74HC/HCT7046A" and I was able to prototype a circuit using a breadboard which works but it is not very stable. In my circuit, C1 is 120pF, R1 3k and R2 is open. First I have noticed that when the VCO control voltage drops below 1V (about VCO output freq 2.5MHz), the VCO ouput frequency drops to some hundreds of Hz. Does this corresponds to the 1.1V voltage limit defined in the datasheet? For some input frequencies, I can see the output frequency oscillating as if the PLL is not locking. I tried different combinations of C1 and R1 but I was not able to improve my circuit. I also noticed that only compare output 1 and 2 work. Is my frequency range specification outside what this component is able to do? Many thanks

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.