Other Parts Discussed in Thread: TMUX1208, P82B715, TCA9617B, P82B96

Hey,

We are experiencing oscillations in our I2C communication system since integrating the TXS0102 level shifter into our design. The oscillations are the result of the one-shot as described in the data sheet section 8.3.3 "it is recommended that this lumped-load capacitance be considered to avoid O.S. retriggering, bus contention, output signal oscillations, or other adverse system-level affects."

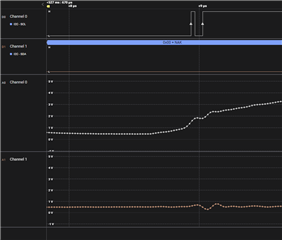

Here is a oscilloscope capture of the oscillation on SCL, and the cross-talk onto SDA.

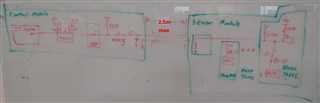

We have several sources of bulk capacitance: ESD diodes, a TMUX1208, 1.25 meters of fixed cabling, a customer selectable additional 1.25m-2.5m of cabling. We estimate 400pF to 800pF of equivalent capacitance. (I can measure it tomorrow.)

When the capacitance is on the high end, we experience this oscillation. We identify this oscillation as a high frequency of I2C communication errors reported by our I2C master controller.

TI Application report "SCEA044–June 2010" titled "A Guide to Voltage Translation With TXS-Type Translators" states: "With capacitive loading >70pF, the TXS-type devices will still successfully operate at lower data rates"

What are the design considerations required to successfully operate this device with capacitive loading >70pF?

Best Wishes,

Erich