Hi

We are using TXS0108E this level translator on our board for TFT display parallel bus interface (DBI-B) at 1MHz frequency.

our MCU is operating at 1.8V and we are level-translating these signals to 3.3V to connect to the TFT display which is configured for 3.3V IO voltage.

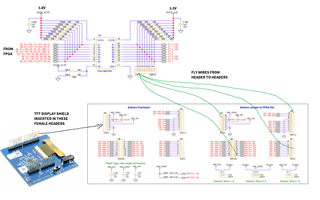

In this case, the TFT display is not fully working properly. Please see attached image.

But when we configure the TFT display IO voltage to 1.8V (i.e. now MCU is also 1.8V and TFT also 1.8V with level translator) display works fine.

Please suggest why this level translator does not work in 1.8V to 3.3V configuration.

Thanks

Santosh