Other Parts Discussed in Thread: SN74AUP3G17, SN65LVDT41, SN74HC14, SN74HCS125, TXU0304

Hello Everyone,

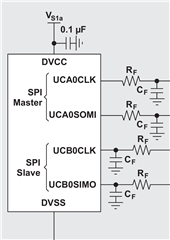

I am working on a project that involves a 1 to 2 meter transmission distance of SPI communication. The application requires transmitting 3200 samples of 16-bit size from 3 axes every second, which amounts to a data rate of approximately 154 kbps.

My SPI configuration includes a single master and single slave setup with 4 wires (MISO, MOSI, SCLK, and CS). I plan to use CAT5 cables for this purpose. Given the cable's inherent characteristics and the distances involved, I anticipate potential challenges with signal integrity due to signal reflections, EMI, and other factors.

To mitigate these challenges and achieve robust SPI communication, I am considering the use of SN74LVC3G17 buffers with Schmitt trigger inputs at both ends of the SPI connection. This buffer is designed to handle a supply voltage from 1.65V to 3.6V and provides over-voltage tolerant inputs, balanced outputs, and is very high-speed compatible (tpd 5-10ns).

I am also contemplating the clock frequency for this configuration. I understand that a lower clock frequency would provide better signal integrity due to lower susceptibility to signal degradation. However, it could also limit the data rate. I am currently considering 0.5 MHz and 2 MHz as potential clock frequencies.

I'd appreciate if anyone can share their experiences, suggestions, or concerns related to the following questions:

1. Is the SN74LVC3G17 a suitable choice for the buffer in this application?

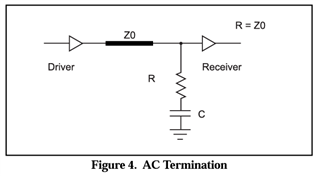

2. What are the key considerations I need to take into account regarding signal reflections, especially when using such buffers in my configuration?

3. Would a clock frequency of 0.5MHz too low of a choice considering the data rate and potential signal integrity issues? Or would 2MHz be more optimal given the configuration?

4. Does anyone have experience or suggestions regarding SPI communication over similar distances, and if so, any specific recommendations or potential pitfalls to avoid?

Thank you in advance for your insights and help!

Best Regards