Hello expert,

Would you please kindly check on below IBIS model setting to see where we can adjust then 3.3V output can generate successfully? Thanks!

Best regards,

Ann Lien

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hey Ann,

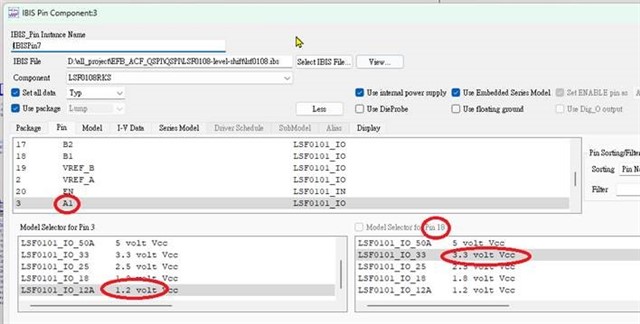

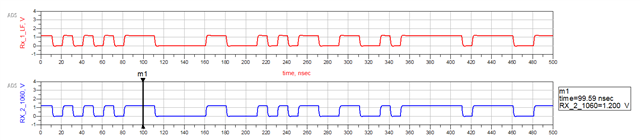

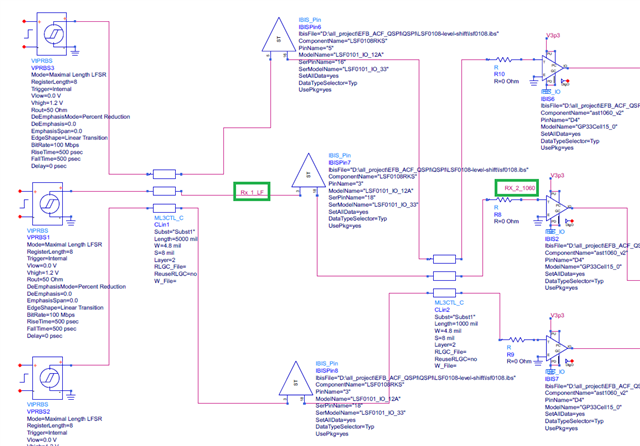

This case looks similar to this E2E thread. Could you try simulating with the input source outputting 3.3V and selecting the same voltage node (3.3V) for both Pin 3 and Pin 18?

Regards,

Jack

Hello Jack,

customer still has two questions below, may you help on it? Thanks!

<1> LSF0108 IBIS cannot simulate 1.2V to 3.3V, right?

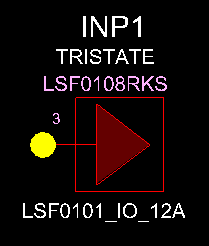

<2>They used Cadence IBIS simulation tool – SigXplore, but import IBIS model in it and it shows only one pin as below. Do you have experience on it?

Best regards,

Ann Lien

Hey Ann,

Yes, you are correct- if they expect to see the behavior of a 3.3V output, a 3.3V model needs to be used for both input and output. However, since this translator performs level shifting passively (unbuffered outputs), it is strongly suggested to not rely on the simulations for testing signal integrity as the results can be unreliable. Usually only buffered I/Os can be accurately modelled with IBIS. I would recommend prototyping the device with the EVMs instead.

I am afraid I do not have experience with SigXplore, so I cannot provide much information on this.

Regards,

Jack