Hi ;

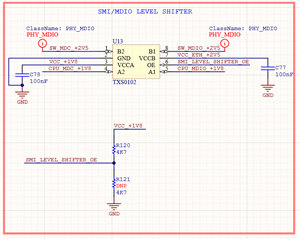

I am using a TXS0102 level shifter in a MDIO line for shifting +1V8 CPU MDIO and +2V5 PHY MDIO.

But sometimes i am encountering accessing issues so i have checked the waveforms and I did not observe any problems. However, I saw that the +2V5 outputs of the TXS0102 started to give output approximately 20 seconds after the CPU started generating the clock, and the line remained at high during these 20 seconds.

What can cause this ? Also do i need to place pulup resistors in MDIO and MDCLK lines ? How can i calculate the pull up values ? According to the datasheet maximum input clamp current is 50mA can low value pull ups exceed this current value and cause damage to the IC?

Thanks