Other Parts Discussed in Thread: SN74HCS165

Hi Team,

Customer says there is a Bug when they use SN74HC165 in new batch board.

They read board ID but there is something wrong.The board ID is 10001101, but what they read is 00011011. Following is their schematic.

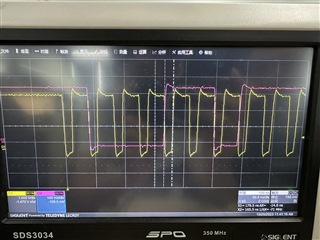

I test their board in old batch, the waveform is following, the hold time is 14ns. In their board the sample point is the rise edge.

Following is their new batch, the hold time is 11ns. That's the main different between the two batch device. And all the device is customer buy after 2Q2022.

We have advise customer to change the PCB or firmware. But it's difficult for them to change those.

Is there any other ways to solve that?

Thanks a lot.