Phenomenon: When using material GTL2014, signal quality issues and reflections were found, which could not be resolved by adjusting the termination resistors. We tried to fit the simulation results, but they did not match the actual measurements and showed significant differences. Therefore, we suspect that there may be something wrong with the simulation.

Question 1: Is it reasonable to use the IBIS model of the 2014 chip as output and the CPU's BUFFER Type as input in the current simulation approach?

Question 2: Should we also include the relevant links of CPLD1 in the simulation? (Previously thought GTL2014 was isolated, so it was not included)

Question 3: Are there equivalent parameter models for the chip?

Remarks:

1. The signal is a voltage signal.

2. The wiring and parameters of vias in the link are considered.

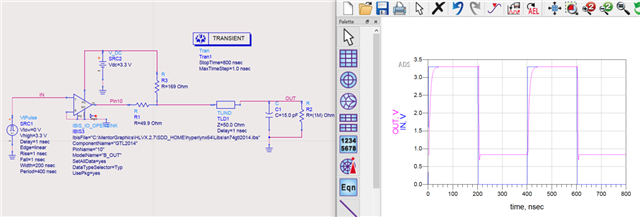

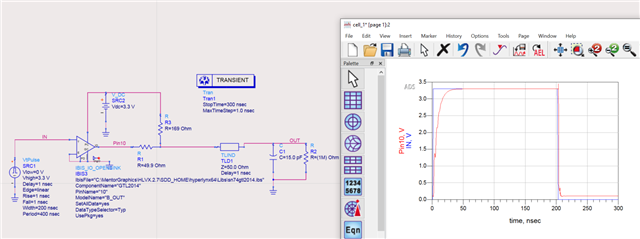

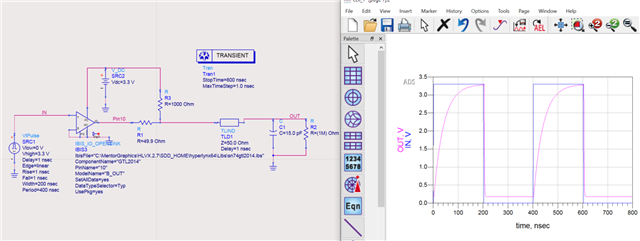

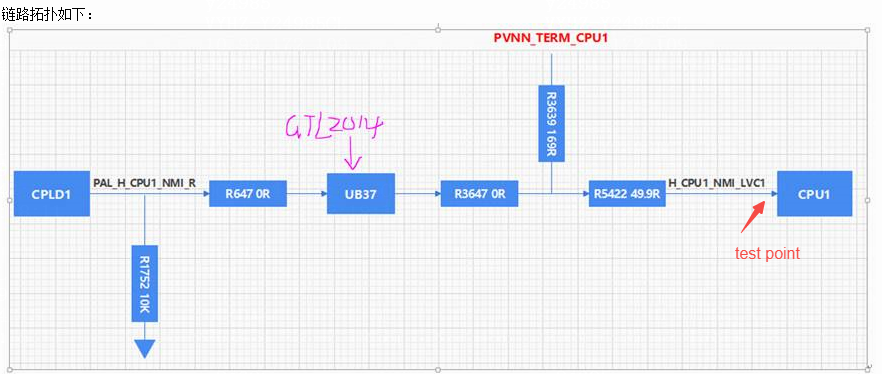

Topology is as follows:

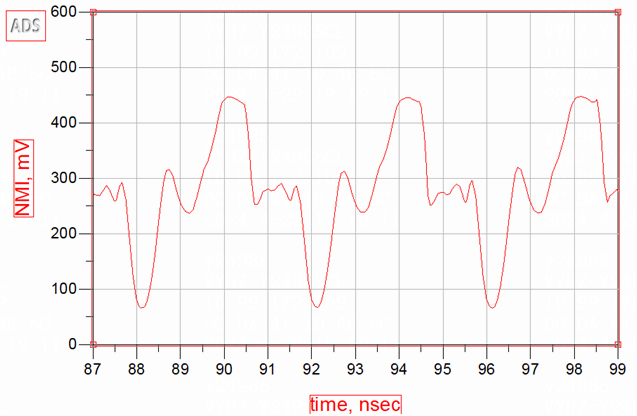

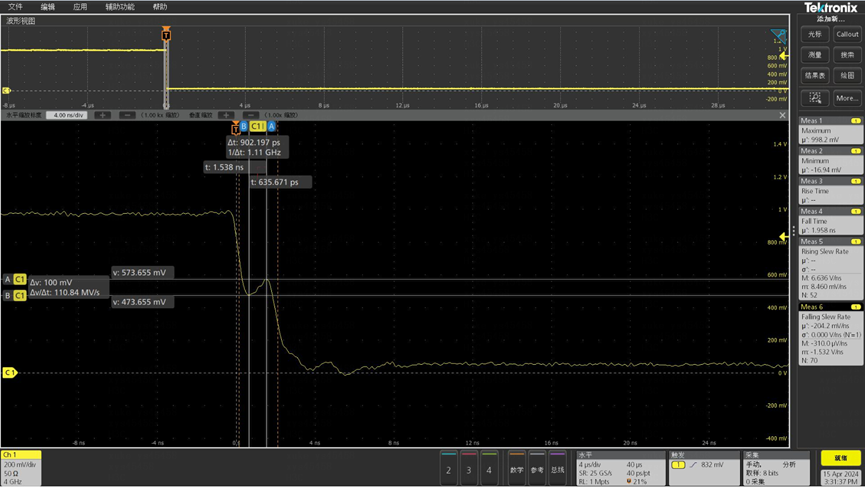

The actual waveform is as follows:

Simulation results: