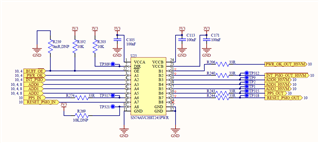

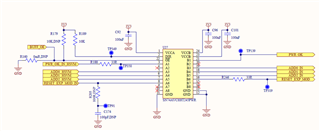

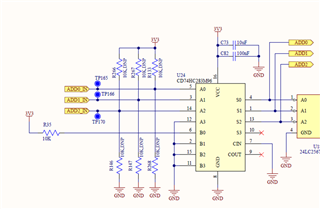

Hi Currently we are using SN74AVCH8T245 8-Bit Dual-Supply Bus Transceiver which has 3.3V RAIL to both VCCA & VCCB and the output being feed to Adder ( CD74HC283M96 ),

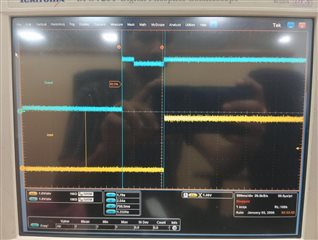

Our requirement is using the Bus transceiver the output bit address is 100 and feeding this input to adder P/N mentioned above and expected output to be 101 and following output signal been feed to controller.

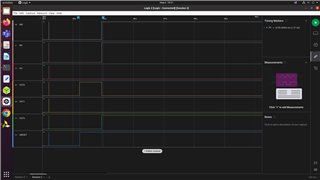

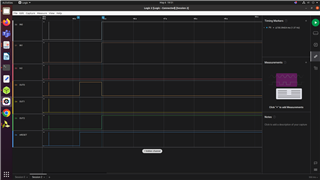

But we are facing an Issue in the inconsistency in the adder output, and not being able to identify where is the issue being caused, Currently we resolved this issue through firmware code by adding 1Sec delay and observed consistency all the time,

I really would like to know if it has to anything with the hardware or where is it going wrong I am attaching the below images of the circuitry.

Please let me know if any further input required,

Thanks.