Tool/software:

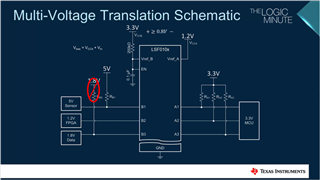

In this video 2:39, For example,I don't understand the reference in the video

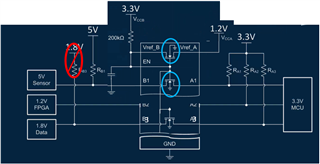

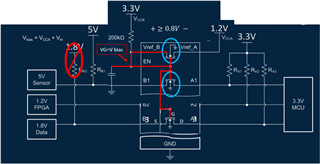

“on the 1.8-volt data line, if the resistor RB3 were removed, any data sent from the MCU would be translated down to 1.2 volts instead of 1.8 volts.”

Where does 1.2V comes from?VccA?