Other Parts Discussed in Thread: TXS0108E, SN74CBTLV3245A

Tool/software:

Hi team

In our system we have multiple boards. All the boards are controlled by the CPU board with AM6442BSEFHAALV processor

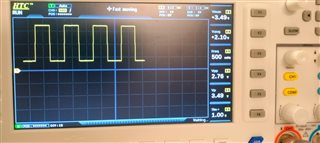

We are using LSF0108RKSR for connecting ARM processor GPIO pins to other boards to ensure fail safe operation . Both the CPU board and the daughter board runs on the 3.3V logic . So we don't need a voltage level transition , and we are using single supply solution (image attached). The issue we are facing is the voltage level at A side pins are clamped by 0.8V . Is there a way to rectify it ?

in our case only a few pins are Bidirectional rest of the pins are either input or output .