Other Parts Discussed in Thread: SN74AXC4T774

Tool/software:

Hi,

I'm trying to run SPI at 50MHz and I need to translate voltages from 1.8V to 1.2V ~ 3.3V.

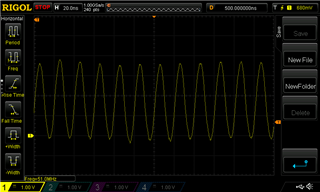

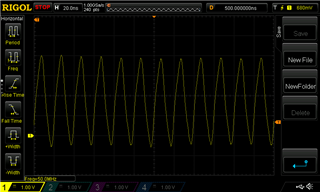

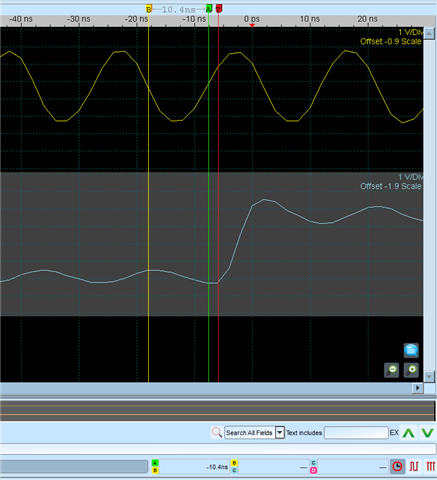

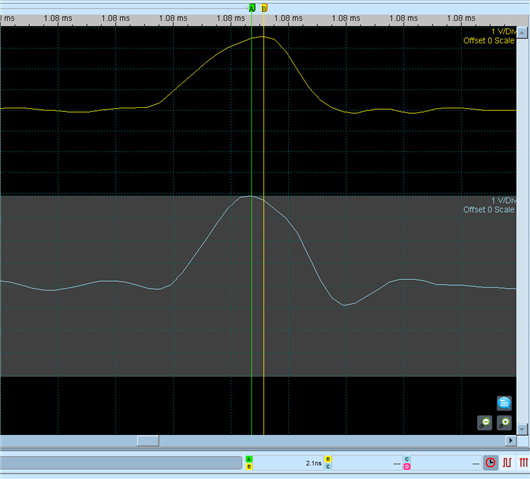

I'm using the SN74AVC4T774 which works perfectly at up to 30MHz, but when going to 50MHz it seems to fail.

Isn't this IC capable of reaching that speed? I'm a bit confused about propagation delay and transition rise and fall.

The first one should be a problem when translating from 1.8V to 1.8V and the rise and fall time (10 ns/V) should be correct to work up to 50MHz, but under those conditions it's not working.

I tried setting the SPI bus to 3.3V and is also not working.

Any piece of advice?

Regards,

P