Other Parts Discussed in Thread: DP83867IR

Tool/software:

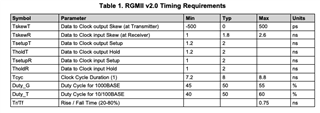

I am curious how to reach the RGMII v2.0 timing specifications when driving RGMII from DP83867IR over TXV0106 level-shifter in Gigabit-Ethernet configuration.

When using the TI-Application Note SNLA243–October 2015 as reference for timing budget of DP83867, I get the following timings:

MAC-Rx Setup = 2ns - Idvar - IOskew = 2ns -0.2ns - 0.35ns = 1.45ns

MAC-Rx Hold = 8ns * (1-0.05-0.5) - 2ns - Idvar - IOskew = 3.6ns - 2ns -0.2ns - 0.35ns = 1.05ns

MAC-Tx Setup = 2ns - Idvar - IOskew - minTsetupRx = 2ns - 0.2ns - 0.35ns - 0.5ns = 0.95ns

MAC-Tx Hold = 8ns * (1-0.05-0.5) - 2ns - Idvar - IOskew - minTholdRx = 3.6ns - 2ns -0.2ns - 0.35ns - 0.25ns = 0.8ns

Now, the TXV0106 level-shifter introduces +/- 0.3ns skew in my application to the timing budget:

MAC-Rx Setup Margin = 1.45ns - 0.3ns = 1.15ns

MAC-Rx Hold Margin = 1.05ns - 0.3ns = 0.75ns

MAC-Tx Setup Margin = 0.95ns - 0.3ns = 0.65ns

MAC-Tx Hold Margin = 0.8ns - 0.3ns = 0.5ns

Trying fitting a MAC/RGMII-driver on a Altera Cyclonve V FPGA fails with this constrains.

For what kind of MAC/RGMII-driver was this level shifter developped? Could you share a system where this TXV0106 is used without violating timing budget?