Tool/software:

Hi, experts.

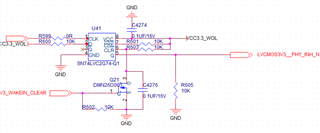

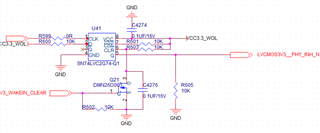

I expect the Q output to be low When the device is powered on, So I use RC delay circuit to make CLEAR pin low firstly ,.Can this design ensure that the power-on output is low? and how much delay should be selected?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi, experts.

I expect the Q output to be low When the device is powered on, So I use RC delay circuit to make CLEAR pin low firstly ,.Can this design ensure that the power-on output is low? and how much delay should be selected?

The minimum supply voltage at which the device is guaranteed to work is 1.65 V. When this voltage has been reached, the /CLR input must be low for at least 6.2 ns.

The delay depends on how fast your supply voltage is rising. When in doubt, check with an oscilloscope, and add a large safety factor.