Tool/software:

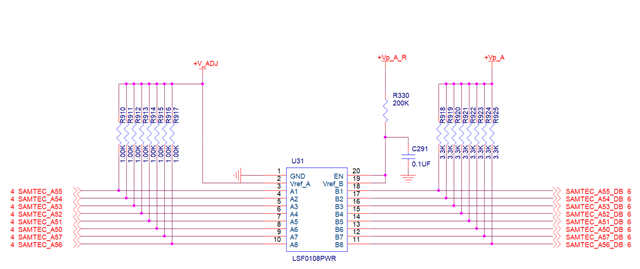

Hello, I'm using LSF0108PWR for level shift. My circuit as below:

The result I want is:

1,When +V_ADJ = 1.2v, +Vp_A_R=1.8V, +Vp_A = 1.8V, Port A's level 1.2V <------> Port B's level is 1.8V.

2,When +V_ADJ = 1.8v, +Vp_A_R=2.5V, +Vp_A = 1.8V, Port A's level 1.8V <------> Port B's level is 1.8V.

3, When +V_ADJ = 1.8v, +Vp_A_R=2.5V, +Vp_A = 2.5V, Port A's level 1.8V <------> Port B's level is 2.5V.

4,When +V_ADJ = 1.8v, +Vp_A_R=3.3V, +Vp_A = 1.8V, Port A's level 1.8V <------> Port B's level is 1.8V.

5, When +V_ADJ = 2.5v, +Vp_A_R=3.3V, +Vp_A = 3.3V, Port A's level 2.5V <------> Port B's level is 3.3V.

6, When +V_ADJ = 2.5v, +Vp_A_R=3.3V, +Vp_A = 2.5V, Port A's level 2.5V <------> Port B's level is 2.5V.

Can the above circuit work for each of the six cases? Thanks!