Tool/software:

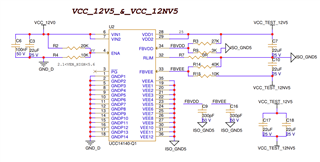

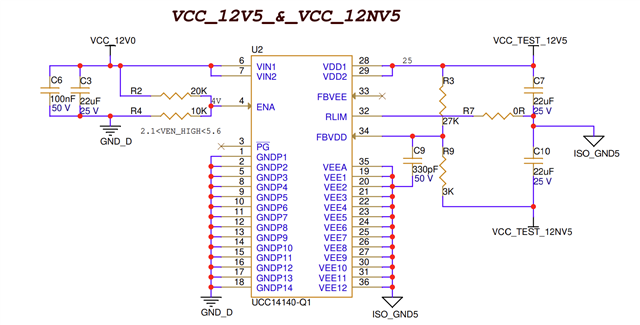

Hi, I am using UCC14140-Q1 to generate both +12.5 and -12.5 and i want same current in both voltage rails

- Will the below circuit work perfectly?

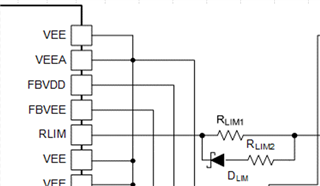

- Did I need to add RLIM and DLIM? if yes can you please suggest me part numbers.

- Should I need to add more capacitor between VCC_TEST_12V5 and ISO_GND5 /ISO_GND5 and VCC_TEST_12NV5

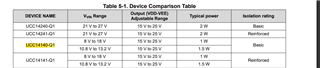

- In the datasheet, it showed that its output will be either 1W or 1.5W. I want to know exactly how much power and current I can expect.

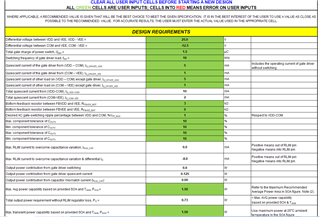

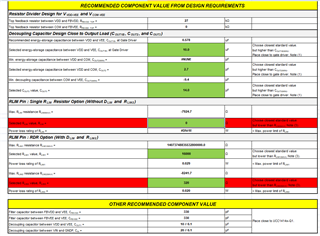

- I have used the UCC14140-Q1 calculator and filled in all the details. Can you tell me if these are correct? If I do not add any Rlim resistor, will it work or not? The calculator shows a warning in red.