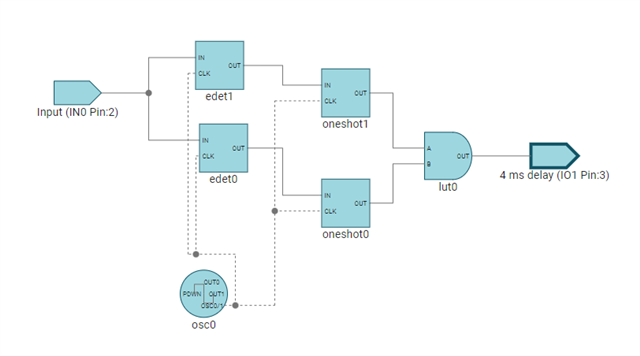

Other Parts Discussed in Thread: TPLD1202

Tool/software:

Hi,

When using edge detection logic devices, I found that the pulse width output when the corresponding edge is detected is 230ns, which is a bit too long for my current design requirements. I want to know how to reduce the width of this pulse.

thanks!