Tool/software:

Hi Team,

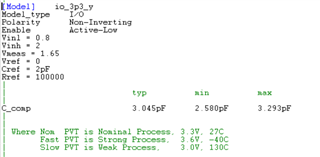

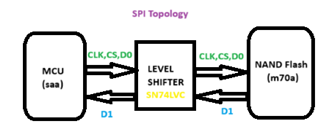

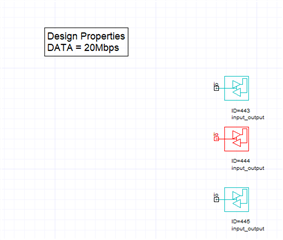

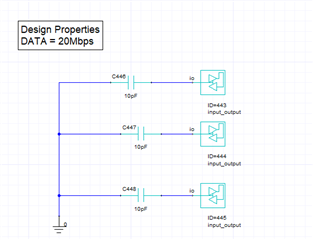

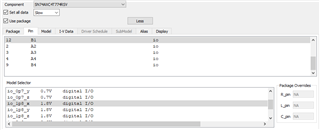

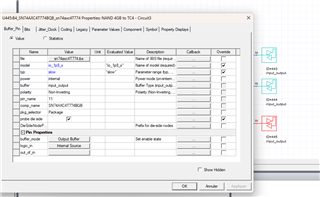

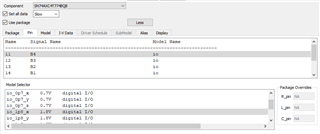

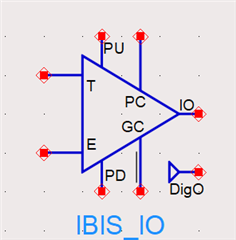

Using the level shifter, we are simulating an SPI interface which translates from 3.3V to 1.8V. @20Mhz

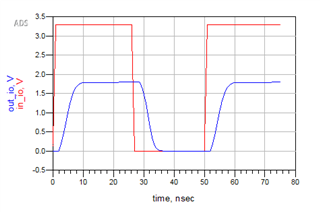

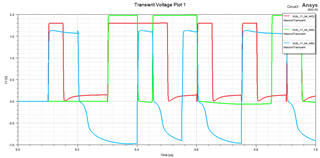

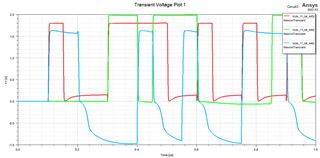

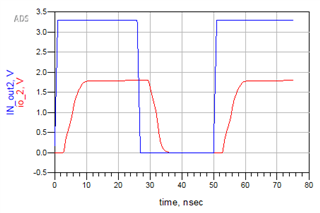

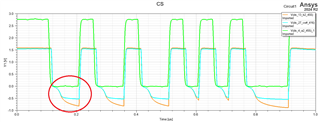

The waveforms at the output of Level shifter seems to be improper.

The signal low seems to be dipping to -0.5V using the IBIS model from the TI website.

And also, this occurs only at Slow corner of the simulation alone.

Please do provide your comments on this.

Thanks and regards,

Sathish Raja C