Tool/software:

レベルシフタ SN74AXC4T774PWR の遅延をオシロで確認したところ、

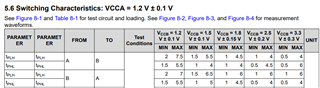

(1) SPI Read:3.3V ⇒ 1.2V バッファ遅延時間 = 28ns

(2) SPI Write:1.2V ⇒ 3.3V バッファ遅延時間 = 14ns

の結果となり、方向により遅延時間に大きな差異が見受けられました。

このことについて以下の質問にご回答お願いいたします。

・方向によって遅延時間が違う場合があるか?

方向によって違う場合、その原因は?(電圧によるものなのか)

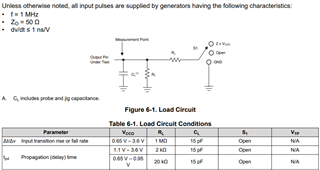

・実測結果が公称値よりも遅延が大きいが、考えられる原因は何か?