Tool/software:

Hi Team,

Please give me your advice on my questions bellow.

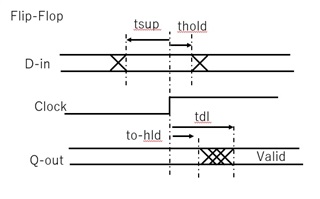

Q1. Can you provide me the timing information on the minimum set up (tsup)

and hold (thold)time of flip-flops relative to the clock.

Q2. Can you provide me the timing information on the minimum output hold (to-hld)

and output delay (tdl) time of flip-flops relative to the clock.

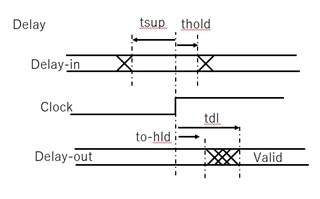

Q3. Can you provide me the timing information on the minimum set up (tsup)

and hold (thold)time of delay/counter relative to the clock.

Q4. Can you provide me the timing information on the minimum output hold (to-hld)

and output delay (tdl) time of delay/conters relative to the clock.

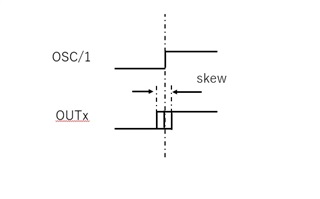

Q5 Can you provide me the maximum skew between OSCx outputs.

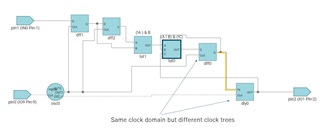

The reason why I came up these questions is that I concern the timing error of my design as attached.

This circuit is a simple example of detecting the edge of an input and make arbitrary delayed one-shot pulse.

The Flip-Flops and delay modules are the same clock domain but on the different clock trees.

If tow clock trees have substantial skew, there is a risk of timing violation resulting unpredictable error.

This kind of error may occur by chance and hard to identify.

So, I want to eliminate such risk in design phase.

Mita