Tool/software:

Dear Forum,

I would like to ask wheter PC2 comparator hf CD74HC4046A is dead-zone free?

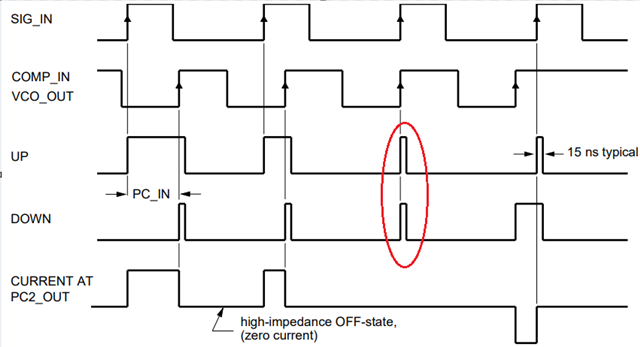

PC2 has a tree-state voltage output and goes to Hi-Z state when PLL reach locked condition (phase difference is 0 deg, after small correnting pulses generated, the best is if correcting pulses can be

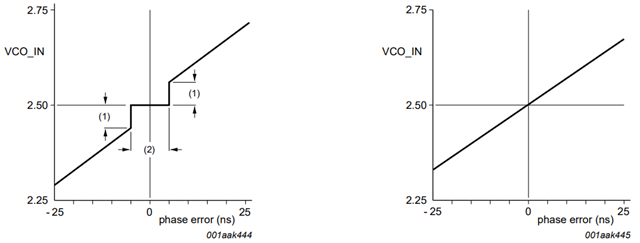

very small too (~less then tpd of a logic gate), ensuring constant senstivity along the entire tuning range without abrupt).

74HCT9046A (no longer produced) exhibits a 'no-dead zone' feature achieved by combination of current output and a technique that internal 'Up' and 'Down' source/sink simulataneosly conducts for a short time.

Is it possible the CD74HC4046 has similar feature (anti-backlash time ->internal D flip-flops async reset is delayed ~10..15ns) despite it is a voltage out device (however, FET current limit ~ current generator)? Because TI document SCAA088 uses the PC2 of 4046A for low phase noise requirement.

Regards,

Joseph