Tool/software:

Hi expert

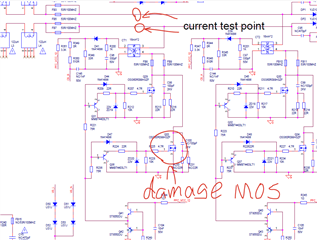

my customer use UCC28070 for a new design, while they did the aging test, there are MOS damage issue. the failure rate is about 2/40.

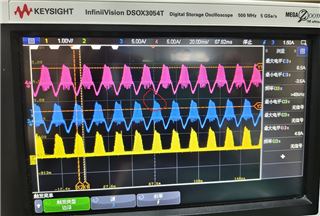

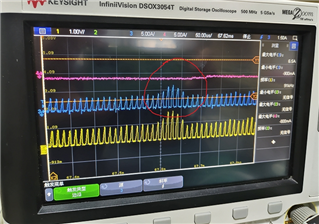

the power is about 650W. VIN=230Vac. The picture is the current result of MOS which test on the issue board(replace new MOS), while output power is higher than 500W, we can capture some of peak current, maybe this is the root cause of the MOS damage. do you have any suggestion of this issue? is this peak current normal?

pink wave is MOS current of channel 1, blue wave is MOS current of channel 2, yellow wave is sample current of channel2