Other Parts Discussed in Thread: SN74HCS00

Tool/software:

Dear Texas Instruments Support Team,

We are experiencing inconsistencies in signal stretching behavior between different batches of the SN74HC00D NAND gate in our product. Specifically, we observed that:

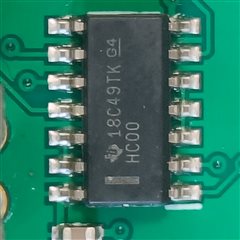

- Older batches with line marking (e.g., TI 38CJJXK HC00, 18C49TK G4 HC00, 2BC8Z9K G4 HC00) exhibit proper stretching of around 4.9 to 5.3 ms.

- Newer batches with dot marking (e.g., 32Z3VYJG3 HC00, TI 38CJJXK HC00) exhibit an increased stretching time of 6.2 to 6.5 ms , deviating from expected behavior.

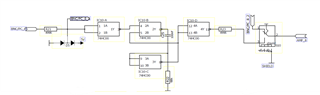

Our setup involves [using SN74HC00D we make signal stretching of 5 ms when needed , e.g., RC delay circuit with (Capacitor, 100nF, X7R, 5% Tol, 0603, 25V, Resistor, 68k, 1% Tol, 0603, with supply voltage 4.92 V)]. Please check below schematic for reference. Also attached images of the Dot marked and Line marked SN74HC00D IC.

We would like to understand:

- Are there any functional differences or internal design changes between these batches?

- Could process variations or different internal die revisions affect propagation delay or threshold behaviour?

- Are there any recommended steps to mitigate these timing differences to ensure consistency?

We appreciate your insights into this matter, as it directly impacts our product performance. Please let us know if additional details or measurements are required.

Thanks in advance