Tool/software:

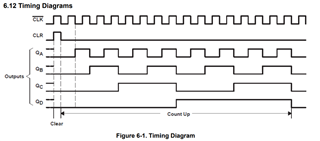

What will the Q_A output be at the first negative edge of CLK after a clear?

When examining the timing diagram (Figure 6.12) in the datasheet, it appears that CLR goes low at the same time that CLK has a negative edge. This makes it unclear whether the first Q_A output after CLR goes low will be 0 or 1.

If the CLR input were to go low half a clock cycle earlier, would the Q outputs remain the same, or would they shift one clock cycle earlier?

Thanks